Tugas :Matakuliah Rangkaian Logika dan Teknik Digital

Dosen Pembimbing : Darwison Daud ,M.T

- Penjumlahan Biner

Penjumlahan biner berbeda dengan penjumlahan bilangan desimal , karena pada biner hanya terdiri dari angka 1 dan 0 saja , sehingga memerlukan operasi khusus untuk melakukan penjumlahannya .pada biner

Gambar 10 .1 :tabel penjumlahan binder dan persoalannya

Berikut adalah contoh dari persoalan mengenai penjumlahan biner.

Gambar 10.2 :persoalan biner dan penyelesaiannya satu-persatu

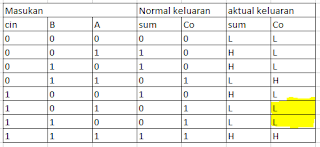

untuk lebih jelasnya mari perhatikan tabel berikut ini ;

Gambar 10.3 Tabel kebenaran dan penjumlahan setengah

Dari tabel diatas dapat diketahui rangkaian sebagai berikut , dan dilambangkan seperti diagram blok berikut;

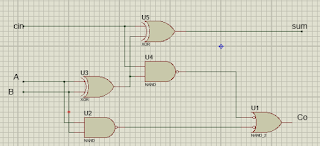

Simulasi rangkaian

Gambar 10.4 : diagram logika penambahan setengah

Rangkaian diatas merupakan rangkaian penjumlahan setengah , berikutnya adalah rangkaian untuk penjumlahan penuh , perbedaannya adalah pada jumlah inputannya , pada penjumlahan setengah terdapat 2 inputan , sedangkan pada penjumlahan penuh terdapat 3 inputan , yaitu biner1, biner2 dan luapan sebelumnya , perhatikan tabel berikut ini ;

tabel tersebut adalah data keluaran dari penjumlahan penuh , dan berikut ini adalah blog diagram dari penjumlahan lengkap , dan bagaimana penjumlahan lengkap dibangun dari penjumlahan setengah beserta rangkaian logika untuk penjumlahan penuh ;

Gambar 10.5 :tabel kebenaran , blok ,dan rangkaian logika penjumlahan penuh

selain menggunakan XOR ,penjumlahan penuh juga bisa dibangun dengan gerbang lain sebagai berikut ini ;

Gambar 10.6 : gerbang penjumlahan penuh dengan gerbang NAND

Dari rangkaian penjumlahan penuh dan penjumlahan setengah , dapat dibangun penjumlahan paralel , berikut adalah contoh diagramnya dan rangkaiannya;

Gambar 10.7 : Penjumlahan 3 bit

2.Pengurangan Biner

Pengurangan biner dikertas dapat dilakukan dengan cara berikut ini

Gambar 10.8 : Pengurangan Biner

sebagai contoh permasalahn lainnya perhatikan penyelesaian berikut ini;

Gamabar 10.10 : persoalan pengurangan biner

Rangkaian pengurangan biner memiliki prinsip keluaran seperti tabel berikut ini ;

Gamabr 10-8 :tabel kebenaran

dari tabel dapat diketahui rangkaiannya sebagai berikut ini;

Gamabr 10-8 :tabel kebenaran

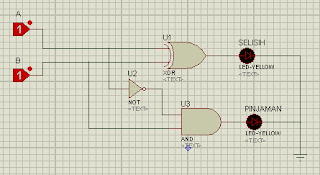

Gamabr 10.9 : blok dan gerbang logika pengurangan setengah

untuk pengurangan penuhnya , kita memerlukan 3 inputan yaitu inputan 1 , inputan 2 , dan inputan pinjaman sebelumnya ,perhatikan tabel berikut ini ;

Gamabr 10.10 : Tabel kebenran pengurangan lengkap

dari tabel kita dapat menggunakan rangkaian berikut ini ;

Gamabar10.11: diagram blok dan gerbang logika untuk pengurangan biner

Untuk penjumlahan lebih dari 1 bit kita dapat merangkai penjulahan setengah pada awal dan penjumlahan penuh setelahnya , dengan inputan luapan dari hasil keluaran luapan dari pengurangan setengah sebelumnya ;

10.12 : Pengurangan biner 4 bit

10.12 : Pengurangan biner 4 bit

Berikut ini adalah beberapa metode yang digunakan dalam pengurangan biner

Gamabar 10.13 : suatu persoalan komplemen 1

selain menggunakan pengurangan setengah dan penguran penuh ,rangkaian pengurangan paralel juga dapat dilakukan dengan rangkaian penjumlahan yang di inverskan, seperti berikut ini;

Gamabar 10.14 : Pengurangan biner dengan menggunakan rangkaian penjumlahan yang diinverskan

Simulasi Rangkaian

3.Rangkaian Untuk Penjumlahan dan Pengurangan Biner

Berikut adalah skema dari rangkaian penjumlahan dan penguran biner , dan beserta rangkaiannya;

Gamabr 3.15 : Kombinasi rangkaian penjumlahan dan pengurangan biner

rangkaian ini memiliki masukan kontrol yang ketika bernilai 1 rangkaian berfugsi sebagai pengurangan , dan ketika bernilai 0 berfungsi untuk penjumlahan.

4.IC Penjumlahan

untuk operasi penjumlahan biner dapat digunakan IC 7483.

Gamabar 10.16 : IC 7483

5. Rangkain Untuk Sistem Penjumlahan dan Pengurangan Biner

Untuk membuat sistem rangkaian penjumlahan atau pengurangan biner digunakan IC penjumlahan dan juga IC register . Seperti Berikut ini

Gamabar 10.17 : rangkaian sistem penjumlahan atau pengurangan biner

6. Perkalian Biner

Perkalian adalah penjumlahan biner sebanyak nilai pengalinya

Gambar 10.18 :Persoalan perkalian desimal

Berikut ini adalah persoalan perkalian biner dan juga gambaran dari hasil persialnya

Gamabar 10.19 : Persoalan biner dan hasil persial keduanya

tidak berbeda jauh dengan perkalian desimal , perkalian biner juga memiliki hasil persial ,berikut adalah gambaran dari hasilnya , dan sebagai contoh permaslahan dari perkalian biner;

Gambar 10.20 : aturan perkalian biner dan contoh penyelesaiannya

pada perkalian biner diketahui bahwa nilai hasil perkalian bilangan dengan 0 adalah 0 , maka suatu perkalian dengan bit terkecil dapat diringkas menjadi berikut ini ;

Gambar 10.21 : Persoalan perkalian

untuk melakukan perkalian biner ada beberapa metoda , yang pertama adala metode penambahan berulang, berikut adalah diagram blok , dan rangkaiannya , beserta taber bagaimana proses perkalian terjadi

Gambar 10.22 : diagram blok perkalian jenis penambahan berulang

Video Simulasi

Gambar 10.23 : mengalikan biner dengan sistem penambahan berulang

metode ini sangat lama melakukan proses , tampak bahwa proses melakukan perkalian dan menjumlahkan dahulu , tidak mengalikan semua bit biner terlebih dahulu , untuk lebih jelasnya perhatikan pada baris ke 5 dari perkalian berikut ini ;

Gambar 10.24 : Persoalan perkalian biner

karena metode jumlah geser memkan waktu , maka digunakanlah metoda tambah geset berikut ini ;

Gambar 10.25 : diagram rangkaian tambah geser dan isi register akumulatornya

Terlihat bahwa proses melakukan penjumlahan dan dan pergeseran sehingga perkalian terjadi lebih sederhana.

8. Notasi Komplemen

Notasi komplement adalah notasi yang digunakan untuk menyatakan bilangan negatif, untuk lebih jelasnya perhatikan skema dan tabel berikut ini

Gambar 10.26 : MSB 4 bit berupa tanda dannilai komplement suatu biner

untuk melakukan proses komplemen dilakukan proses sebagai berikut

Gambar10.27: proses mengkomplent 2

untuk lebih menambah pemahaman , perhatikan penyelesaian dari penjumlahan dengan bilangan bernotasi dan penyelsaian dari pengurangan dengan bilangan bernitasi berikut ini;

Gambar 10.28 dan Gambar 10.29 :Persoalan penjumlahan dan pengurangan biner bertanda

9 . Rangkain untuk penjumlahan dan penguranga dengan metode komplemnt

tidak berbeda jauh dengan rangkaian yang digunakan untuk penjumlahan atau pengurangan biner , rangkaian ini juga memiliki masukan kontrol dan bit yang akan mengalami operasi , tetapi yang membedakannya adalah keluaran carry dari rangkaian penjumlahan penuh terakhir tidak diumpankan kepada rangkaian penjumlahan yang diawal .

Gambar 10.30 : Rangkain untuk komplemen 2

10. Mencari kerusakan pada rangkaian

Berikut adalah rangkaian dari penjumlahan penuh dan contoh dari kesalahan yang terjadi

Gambar 10.31 : Contoh kesalahan yang terjadi pada rangkaian

untuk mencari kesalah yang terjadi pada rangkain , terlebih dahulu diperiksa apakah setiap IC yang digunakan berjalan dengan baik , periksa IC dengan menggunakan tabel kebenaran . karena tabel kebenaran akan menggambarkan bagaimana rangkaian itu harusnya berjalan .

Tidak ada komentar:

Posting Komentar